# Application of Parallel Processing - A Case Study on FPGA based on Reconfigurable Computer

Nur Izni Syahirah binti Hassim<sup>#1</sup>, Mohamed Faidz Mohamed Said<sup>#2</sup>

# Faculty of Computer & Mathematical Sciences, Universiti Teknologi MARA 70300 Seremban, Negeri Sembilan, MALAYSIA <sup>1</sup> nurznihassim@gmail.com

<sup>2</sup> faidzms@ieee.org

Abstract—Reconfigurable computing is an assuring technology that accommodates the present and future computational demands. An example of the extreme notch of parallelism created in reconfigurable hardware materials is the field programmable gate arrays (FPGAs). Though, despite their capable performance, reconfigurable computers are still to be widely applied. It is because reconfigurable computer has the lack of mutual and intuitive operating system. The goal of this research is to explore the feasibility of providing a systematic processing and to understand the view into reconfigurable computer through Operating System without incurring significant performance penalties. Comportment of hardware is the key characteristic of Reconfigurable Computing is that it can be reconfigured to be applied in a particular functionality that is more suitable for specifically fitted in hardware than on a simple uniprocessor. Reconfigurable computing systems connect with the programmable hardware and microprocessors, in order to have the improvement of the combined strengths of software and hardware that will be used in applications alternating from embedded systems to high performance computing.

# *Keywords*: Field Programmable Gate Arrays, FPGA, configurable computer

# I. INTRODUCTION

Nowadays the rising demand for global connectivity that day by days become more powerful and extraordinary will lead to new satellite system ideas [1]. Most likely, today satellite communication in this world is based on flexible payload with Digital with Digital Transparent Processor (DTPs) or simple bent-pipe. The DTPs are sometime based on one-time programmable FPGA [2]. There are also, the earths of study sensor that will create a lot of data than it can be downloaded in real time by a ground station. The first is to accomplish data extraction and data processing on board the satellites and then only conduct the result [3]. By using FPGAs also, a flight experiment evaluation can be developed. As the development of space capabilities grows, so the resulting data needed to be managed is a lot [4]. A dynamically Reconfigurable FPGA-based computer are found in Erlangen Slot machine [5]. Growing capacities provided by FPGAs have made them the ultimate choice for reconfigurable computing platforms. It has made the greatest choices for reconfigurable computing stages. FPGA is used for improvement in computation and the efficiency by time allocation resources on the devices [5]. With increase of amount of samples, consumption of hardware resources is not obvious, and computation speed is still at a high level [6]. To design a built-in FPGAs reliability, a grained 2-D error corrections codes are being used. To reduce the correction time and improve the reliability of FPGA, an ECC using encode and compare is proposed [7]. The system on chip design are using FPGA based many cores. It will result in to better satisfy the requirements of highly demand applications [8].

# II. PROBLEM STATEMENT

In order to use or create an application or system based on FPGAs, that can be used in software computing technique and analysis as an application [9], Gate Arrays have been the best method in designing a circuit that are smaller. Computational scientist aggressively seeks floating towards an application performances improvement. Reconfigurable computing (RC) based on Field Programmable Gate Array (FPGA) technologies one of the technologies that have the ability to yield performances development for many computing demanding task [10]. Satellite imaging loads mostly operate a store-and-forward device, where by the captured images are positioned on board and transmitted to ground later. Transmission system is one of the main areas in which digital signal processing finds thru the application. Currently, the advances in signal processing have helped hugely by reducing the difficulty of communication system design [11].

# III. METHODOLGY

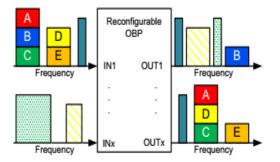

In all transmission systems used in satellite, a medium is the most important resource. It also has numerous different aspects for the indicator of processing that can be executed well [12]. Figure 1 shows the basic design of FPGA-based architecture. This design indicates the following signal processing potentials:

- layer processing (e.g. IP-based)

- Physical layer routing

- Physical layer processing

These signal managing potentials are used for related situations such as broadcaster.

Figure 1. Basic architecture of FPGA-based [12]

#### System correction

Image compression system attempt when transfer a number of bits that demonstrate the true data in the scene and it is also able to reduce the low information areas because there are fewer details that exist. To avoid moving large cloud-covered areas, on-board system is implemented on the satellite probably to remove large cloud-covered areas before passing the data. FPGAs-based hardware accelerators can be used to efficiently handle compute-intensive applications like image processing due to their high inherent parallelism [13].

#### *Use Case and the Application:*

Transmissions satellites nowadays are focused only towards specific such as:

- IP-based transmission

- Broadcast or Direct-To-Home (DTH)

- Worldwide mobile transmission

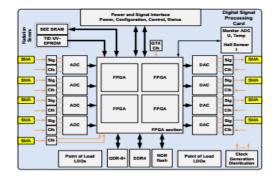

Different procedures are used for different transmissions system which will not fit with other systems. No common standard and the practical development is minimalized due to the circumstance. Another main benefit of reconfigurable time is optimized production/development process. FPGA is organized after control on reset by transferring the full bit file straight from every programmable read only memory (PROM) [14]. There are Board Processing that are based on reconfigurable FPGAs. While the hardware is in production, FPGA design can be developed.

#### Flexible On Board Processing (OBP)

The obligation groups for On Board Processing are flexibility and dependability. The performance flexibility is being satisfied by using newest reconfigurable FPGAs. The hardware malfunction rate can be analysed to achieve a dependable design. FPGAs are not enhanced for a particular application due to their flexibility.

Figure 2. Block Diagram that contain FPGA [14]

#### IV. RESULT

In FPGA, the soft-core processor is worked for the conjunction with the offered hardware. This choice was discovered, and the result showed that in real time requirement the soft-core processors are slower. Second solution is advanced performance is used in microprocessor at conjunction with keen hardware in FPGAs. This will result in meeting the strict real-time conditions and stability between high performance and configurability [16-18]. Hence this can be deduced that those solutions can be ensuring in preserve good visual appearances of imagery.

## V. CONCLUSION

Field Programmable Gate Arrays (FPGAs) is a convincing technology of parallel reconfigurable computing that accommodates the present and future computational demands. In this paper, FPGA is used in communication satellite system as well as in processing image system. The FPGA designed system is proven to successfully work in producing better communication or producing decent image when detecting blurring image while FPGA is used as the base of the satellite system.

#### References

- Hofmann, A., et al. Reconfigurable on-board processing for flexible satellite communication systems using FPGAs. in Internet of Space (TWIOS), Topical Workshop on. 2017. IEEE.

- [2] Kuwahara, T., et al., FPGA-based operational concept and payload data processing for the Flying Laptop satellite. Acta Astronautica, 2009. 65(11–12): p. 1616-1627.

- [3] Mostert, S. and E. Kriegler, Implementing an image processing system for the next generation Earth observation sensors for the SUNSAT 2 micro-satellite programme. Acta Astronautica, 2005. 56(1): p. 171-174.

- [4] Schmidt, A.G. and T. Flatley, Radiation Hardening by Software Techniques on FPGAs: Flight Experiment Evaluation and Results. 2017.

- [5] Majer, M., et al., The Erlangen Slot Machine: A dynamically reconfigurable FPGA-based computer. The Journal of VLSI Signal Processing Systems for Signal, Image, and Video Technology, 2007. 47(1): p. 15-31.

- [6] Liu, H., Y. Zhao, and G. Xie. Image segmentation implementation based on FPGA and SVM. in 2017 3rd International Conference on Control, Automation and Robotics (ICCAR). 2017.

- [7] Ahilan, A. and P. Deepa, Design for built-in FPGA reliability via fine-grained 2-D error correction codes. Microelectronics Reliability, 2015. 55(9–10): p. 2108-2112.

- [8] Baklouti, M., et al., FPGA-based many-core System-on-Chip design. Microprocessors and Microsystems, 2015. 39(4): p. 302-312.

- [9] Laxmi, V., C.S. Adiga, and S. Harish. FPGA based Reconfigurable Computing Systems: A New Design Approach-A Review. in Advanced Materials Research. 2012. Trans Tech Publ.

- [10] Kindratenko, V. and D. Pointer. A case study in porting a production scientific supercomputing application to a reconfigurable computer. in 2006 14th Annual IEEE Symposium on Field-Programmable Custom Computing Machines. 2006.

- [11] Nivin, R., J.S. Rani, and P. Vidhya. Design and hardware implementation of reconfigurable nano satellite communication system using FPGA based SDR for FM/FSK demodulation and BPSK modulation. in 2016 International Conference on Communication Systems and Networks (ComNet). 2016.

- [12] Sharma, S., et al. FPGA Implementation of M-PSK Modulators for Satellite Communication. in 2010 International Conference on Advances in Recent Technologies in Communication and Computing. 2010.

- [13] Irwansyah, A., et al., FPGA-based multi-robot tracking. Journal of Parallel and Distributed Computing, 2017. 107: p. 146-161.

- [14] Mandal, S., et al., Efficient dynamic priority based soft error mitigation techniques for configuration memory of FPGA hardware. Microprocessors and Microsystems, 2017. 51: p. 313-330.

- [15]

- https://www.youtube.com/watch?v=D3vD4d5LfbQ&rel=0

- [16] M. F. M. Said, M. N. Taib, and S. Yahya, "Analysis of the CPU Utilization for Point-to-Point Communication Operations in a Beowulf Cluster System," in 2008 International Symposium on Information Technology, 2008, pp. 1-6.

[17] M. F. M. Said, M. N. Taib, and S. Yahya, "Analysis of TCP/IP

- [17] M. F. M. Said, M. N. Taib, and S. Yahya, "Analysis of TCP/IP Overhead on Overlapping Message Transfer and Computation in a Distributed Memory System Architecture," International Journal of Advanced Research in Computer Science (IJARCS), vol. 3, pp. 22-36, 2012.

- [18] M. F. M. Said, S. Yahya, and M. N. Taib, "Analysis of Different Programming Primitives used in a Beowulf Cluster," International Journal of Computer and Information Technology (IJCIT), vol. 1, pp. 25-33, 2012.