# Instruction-level Parallelism - A Case Study on Software Approach

Nur Asilah Agus Salim<sup>#1</sup>, Mohamed Faidz Mohamed Said<sup>#2</sup>

<sup>#</sup> Faculty of Computer and Mathematical Sciences, Universiti Teknologi MARA 70300 Seremban, Negeri Sembilan, MALAYSIA

<sup>1</sup> asilahagus10@gmail.com

<sup>2</sup> faidzms@ieee.org

Abstract—Determining how one instruction relates to another is to exploit in an instruction level parallelism (ILP). It is generating more information about the instruction sequence and thus involving more factors in optimizing the instruction sequence. Some of the articles that have been reviewed discuss the differences between hardware and software in this instruction level parallelism. Conventional processor outlines that issue and executes at most one operation for each cycle. These are regularly called scalar plans. Static and dynamic planning procedures have been utilized to accomplish superior to scalar execution by issuing and executing more than one operation for every cycle. Likewise, this will identify the methods that use software approach in application of real life. A fascinating road for future research is to consider what primitives should to be upheld in hardware by advertising the adaptability of software-based approaches. The amount ILP exists in programs is extremely application particular. In specific fields such as designs and logical registering, the sum can be large. Finally, the workloads such as cryptography may show a great deal less parallelism.

#### Keyword: software, hardware, parallelism, static, dynamic

## I. INTRODUCTION

Instruction level parallelism (ILP) is a gathering of processor and compiler plot frameworks that quicken execution by making solitary machine operations execute in parallel. In spite of the fact that ILP has showed up in the most noteworthy execution uniprocessors for as long as 30 years, the 1980s saw it turn into a considerably greater drive in PC plan. A few frameworks were assembled, and sold monetarily, which drove ILP a long way past where it had been some time recently, both as far as the measure of ILP offered and in the focal part ILP played in the plan of the framework. Before the decade is over, cutting edge microchip plan at all significant CPU producers had fused ILP, and new systems for ILP have turned into a well-known theme at scholastic conferences [1]. Current usage of out-of-order execution dynamically remove ILP from customary projects. Out-of-order execution refers to while the program is executing and with no assistance from the compiler. An option is to separate this parallelism at assemble time and by one means or another pass on this data to the equipment. Because of the many-sided quality of scaling the out-of-order execution strategy, the industry has re-evaluated guideline sets which unequivocally encode various free operations per instruction [2]. Dataflow

architectures are another class of architectures where ILP is explicitly specified [3].

#### II. DEFINITION

Instruction level parallelism is a measure of what number of the operations in a PC program can be performed all the while. The cover among instructions or block is called instruction level parallelism. There could be a loop, a conditional, or some other valid sequence of statement. Goal of compiler and processor designers implementing instructionlevel parallelism is to identify and take advantage of as much instruction-level parallelism as possible [4]. This effort is to accomplish the genuine execution of more than one direction at any given time through dynamic scheduling and how to boost the throughput of a processor. It will be helpful to return to the different conditions and perils once more, sometime recently talking about these all the more capable methods for distinguishing and misusing more ILP [2].

## III. DISCUSSION

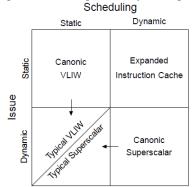

Reciprocal approach is the utilization of static planning methods to misuse a similar parallelism. In this paper [5], a portion of the trade-offs is portrayed between the utilization of static and dynamic planning procedures. Statically planned processors require that the latencies of all operations be settled and known ahead of time. Since statically booked processors do not bolster dynamic dependency identification, this confinement constrains the progressions that can be made in a design to those which do not influence operation latencies. These outcomes demonstrate that the kind of static schedule is essential just with practically zero dynamic analysis equipment - in this area the very much coordinated calendar is unfathomably better than both under matched and overmatched plans [5]. The changes ought to revamp code, from information accessible statically at incorporate time and from the insight into the hidden hardware. Software pipelining is an enhancement that can enhance the loop executionexecution of any framework that permits instruction-level parallelism (ILP), including VLIW and superscalar designs. Increment execution is done by scheduling directions from various iteration into a solitary emphasis of the loop. It determines its execution pick up by filling delays inside every iteration of a loop body with guidelines from various emphases of that same loop [4]. However, the resource constraint and the loop carried dependences make the software

pipelining issue extremely confounded and troublesome so the current software pipelining methodologies cannot get a tasteful time and space effectiveness with low calculation unpredictability [6]. For communicating parallelism and territory, the key difficulties are the capacity to uncover the majority of the inherent parallelism. The programming model will guarantee that the declaration of parallelism and territory is convenient over a scope of frameworks [7].

# A. Different between Software and Hardware

The product level chips away at static parallelism. Static parallelism implies the compiler chooses which guidelines to execute in parallel. The Itanium processor takes a shot at the static level parallelism. Hardware level works upon dynamic parallelism though. Dynamic parallelism implies the processor chooses at run time which direction to execute in parallel. The Pentium processor takes a shot at the dynamic succession of parallel execution [5]. The majority of programming is composed in high level programming language that are less demanding and more effective for developers, which means more like a natural language [8]. Like forceful hardware based theory frameworks, this approach is to determine all name conditions through renaming and furthermore some stream information conditions through sending by monitoring reliance infringement on the granularity of single factors [9].

Fig. 1. Instruction-level parallel schedule-issue regions [5]

Fig. 2. A diagram shows the interaction between user and software in typical desktop computer [8]

## B. Methods Approach in Software

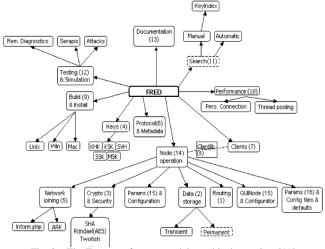

One of the paper review discusses about the advantages of such a scientific establishment [10], to the point that go a long way past the utilization of alleged formal strategies for the particular and verification of software. Formal strategies have been viewed as approaches to enhance the nature of the product improvement process. They examine the advance in formal techniques and their impact in shaping a logical establishment for software innovation [10]. The second paper review, examined joining and early commitment to the aggregate activity of open source programming development. Utilizing information from Freenet, the researchers inductively created hypothesis on the periods of joining a designer group and making the underlying commitments to the software [11].

Fig. 3. The Freenet reference model-graphical overview [11]

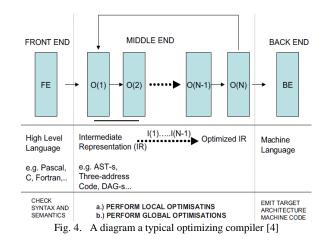

In the third paper review [4], they take a gander at compiler-based scheduling, which is otherwise called static planning if the hardware does not along these lines reorder the direction succession created by the compiler. Assemble time enhancements give various investigation serious improvements that generally could not be performed at run time because of the high overhead connected with the examination. Compilers can rearrange code with the end goal that more ILP is uncovered for further improvement or misuse at run time [4].

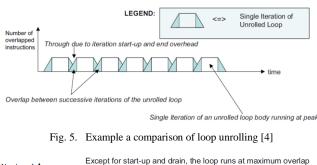

Fig. 5. and Fig. 6. display the comparison between software pipelining and loop unrolling. The different of time is

significant where loop unrolling have overlapped between successive iterations of the unrolled loop.

Fig. 6. Example of a comparison of software pipelining [4]

Lastly, the goal of this paper [12] is to recognize the current software security approaches utilized as a part of the software development lifecycle (SDLC). With a specific end goal to meet their objective, they directed a deliberate mapping study to recognize the essential reviews on the utilization of software security methods in SDLC. The outcomes demonstrate that as often as possible, most utilized methodologies are static examination and dynamic investigation that give security checks in the coding stage. Also, the outcomes demonstrate that many reviews in this survey considered security checks around the coding phase of software development. This work will help programming improvement associations in better understanding on the current programming security approaches utilized as a part of the software development lifecycle [12]. In another research paper [13], they present their approach to the introduction of software architecting activities in an agile project course. The approach is based on literature sources and is customized to fit the instructive objectives and setting. Using this approach, students perceive the value of the architecting activities and see the approach as complementary to agile software development [13]. The process of making an individual software is called product customization or also called product derivation, in which the core activity is selecting a suitable feature set which satisfies certain specified requirements [14]. Convey spare MP permits convey free calculations which, furthermore of being less difficult, uncovered more inherent instruction level parallelism. There is a tradeoff, where more SCS digits are expected to achieve guaranteed exactness than in the thick high-radix case, because of the held bits. Hence more elementary operations will be required [15].

Fig. 7. Partial feature of web portal [14]

#### IV. CONCLUSION

This paper shows a cycle of constantly enhancing benchmarks. The benchmark upgrades change the genuine creation of software in terms of instruction level parallelism. Everything relies upon how the illustrative of average workloads the benchmarks are. Some have proposed another product based on the way to deal with the string level information reliance theory framework in which the key target has been to accomplish low programming overheads. It might be securely expected that future processors will offer considerably more parallelism. This may appear as more profound pipeline is not a long way from being achieved.

#### REFERENCES

- B. R. Rau and J. A. Fisher, "Instruction-level parallel processing: history, overview, and perspective," *The journal of Supercomputing*, vol. 7, no. 1-2, pp. 9-50, 1993.

- [2] G. van der Linden, "Instruction-level Parallelism," 2006.

- [3] N. A. S. Asilah. "170526 CSC580 NAAS Youtube." https://www.youtube.com/watch?v=rtxQVQgK5m0 (accessed.

- [4] B. Savkovic, "Software Approaches to Exploiting Instruction Level Parallelism," 2004.

- [5] K. W. Rudd and M. J. Flynn, "Instruction-level parallel processors-dynamic and static scheduling tradeoffs," in *Parallel Algorithms/Architecture Synthesis*, 1997. Proceedings., Second Aizu International Symposium, 1997: IEEE, pp. 74-81.

- [6] J. Wang, C. Eisenbeis, M. Jourdan, and B. Su, "Decomposed Software Pipelining: A New Approach to Exploit Instruction Level Parallelism for Loop Programs," in Architectures and Compilation Techniques for Fine and Medium Grain Parallelism, 1993: Citeseer, pp. 3-14.

- [7] V. Sarkar, W. Harrod, and A. E. Snavely, "Software challenges in extreme scale systems," in *Journal of Physics: Conference Series*, 2009, vol. 180, no. 1: IOP Publishing, p. 012045.

- [8] Wikipedia. "Software." <u>https://en.wikipedia.org/wiki/Software</u> (accessed.

- [9] P. Rundberg and P. Stenström, "An all-software thread-level data dependence speculation system for multiprocessors," *Journal of Instruction-Level Parallelism*, vol. 3, no. 1, p. 2002, 2001.

- [10] M. Broy, "Software technology—formal methods and scientific foundations," *Information and software technology*, vol. 41, no. 14, pp. 947-950, 1999.

- [11] G. Von Krogh, S. Spaeth, and K. R. Lakhani, "Community, joining, and specialization in open source software innovation: a case study," *Research Policy*, vol. 32, no. 7, pp. 1217-1241, 2003.

- [12] N. M. Mohammed, M. Niazi, M. Alshayeb, and S. Mahmood, "Exploring software security approaches in software development lifecycle: A systematic mapping study," *Computer Standards & Interfaces*, vol. 50, pp. 107-115, 2017.

- [13] S. Angelov and P. de Beer, "Designing and applying an approach to software architecting in agile projects in education," *Journal of Systems and Software*, vol. 127, pp. 78-90, 2017.

- [14]

- X. Lian, L. Zhang, J. Jiang, and W. Goss, "An approach for optimized feature selection in large-scale software product lines," *Journal of Systems and Software*, 2017.

D. Defour and F. De Dinechin, "Software carry-save: A case study for instruction-level parallelism," in *International Conference on Parallel Computing Technologies*, 2003: Springer, pp. 207-214. [15]